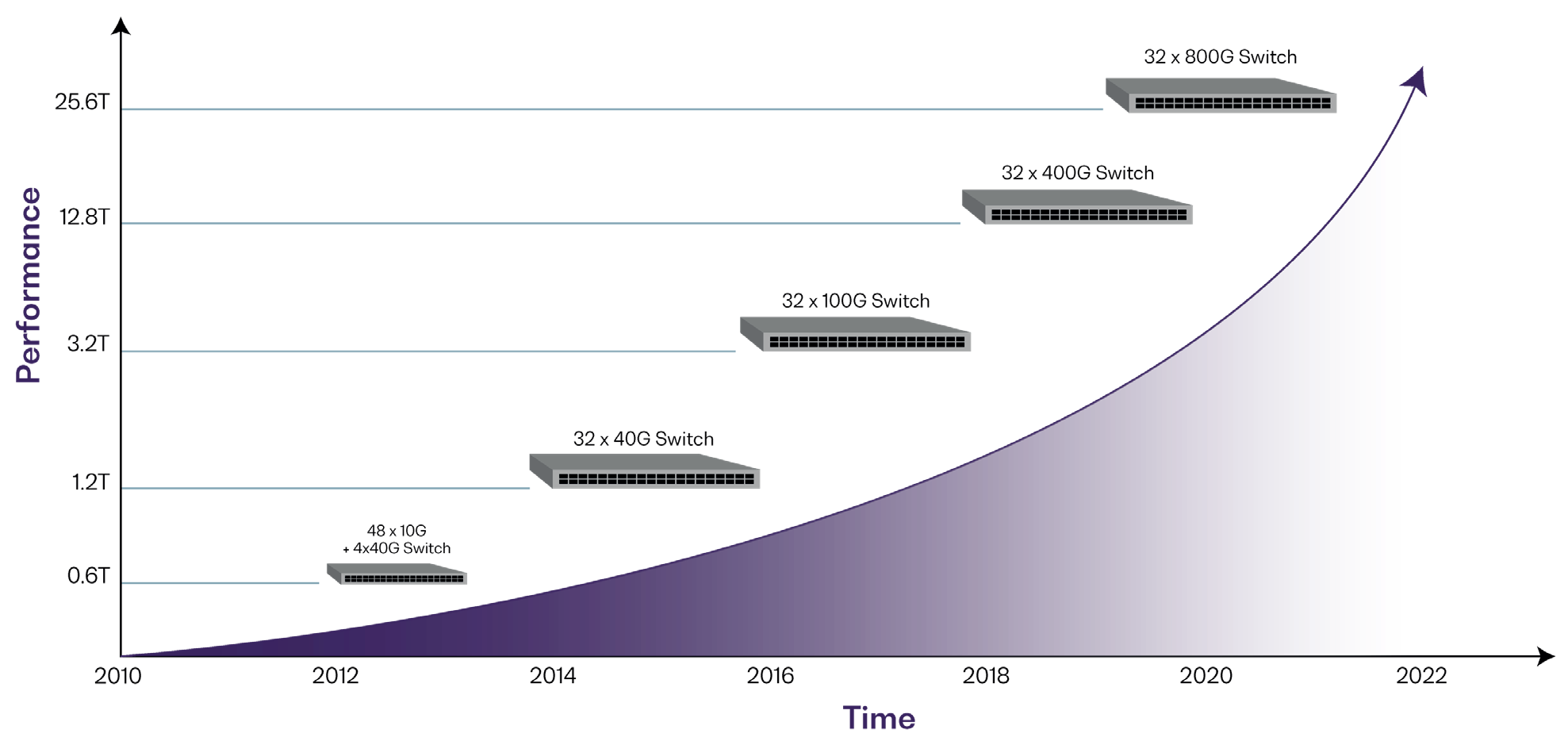

隨著數(shù)據(jù)中心、機(jī)器學(xué)習(xí)和人工智能(AI)應(yīng)用的快速發(fā)展,網(wǎng)絡(luò)設(shè)備需要快速傳輸大量數(shù)據(jù)。因此,網(wǎng)絡(luò)交換機(jī)的帶寬需求在過去十年中增長了超過8000%。如圖1所示,交換機(jī)的速度需求從2010年的320Gb/s增長到2022年的25.6Tb/s,并且很快將需要超過51.2Tb/s的帶寬。

圖1為了支持?jǐn)?shù)據(jù)密集型應(yīng)用,光設(shè)備的需求快速增長,推動了對更高性能、更高帶寬網(wǎng)絡(luò)交換機(jī)的需求。

如果繼續(xù)使用當(dāng)前的可插拔模塊方法(即將模塊插入機(jī)架式交換機(jī)的前面板),實現(xiàn)超過25.6Tb/s的高通道數(shù)將極具挑戰(zhàn)性。在這些高帶寬下使用可插拔模塊會導(dǎo)致在將電信號從前面板后方傳輸?shù)浇粨Q機(jī)ASIC(應(yīng)用特定集成電路)時出現(xiàn)較大的能量損失,并且需要高功耗的信號處理來克服通道損傷。這些問題直接導(dǎo)致了高功耗以及與冷卻可插拔光收發(fā)器和交換機(jī)相關(guān)的高運(yùn)營成本。

為了應(yīng)對這些挑戰(zhàn),消除數(shù)據(jù)傳輸瓶頸,光工程師正在開發(fā)更高效的方法,將光通道更接近電子設(shè)備。許多大型科技公司和光標(biāo)準(zhǔn)組織支持將收發(fā)器從前面板移除,創(chuàng)建一個將數(shù)據(jù)直接傳輸?shù)诫姎饨粨Q結(jié)構(gòu)的單一封裝設(shè)備。這種技術(shù)被稱為共封裝光學(xué)(CPO)設(shè)備,可以在不顯著增加功耗或收發(fā)器占地面積的情況下增加帶寬,因為光學(xué)和電子元件直接相鄰,位于同一個封裝組件中。這種設(shè)計最小化了傳輸損耗,降低了信號處理需求,提供了最低的每比特數(shù)據(jù)傳輸功耗。

與任何新技術(shù)一樣,工程師不僅需要解決開發(fā)這些實際設(shè)備的復(fù)雜性,還需要具備能夠快速測試這些高通道密度設(shè)備功能的儀器。

本文檔概述了正在進(jìn)行的工作,以確保共封裝光學(xué)設(shè)備在各種高帶寬應(yīng)用中的互操作性,并討論了如何應(yīng)對這一新技術(shù)帶來的測試挑戰(zhàn)。

確保共封裝光學(xué)(CPO)設(shè)備的互操作性與標(biāo)準(zhǔn)化

目前,光互連論壇(Optical Internetworking Forum,簡稱OIF)和板載光學(xué)聯(lián)盟(Consortium for On-Board Optics,簡稱COBO)正在迭代共封裝光學(xué)設(shè)備開發(fā)的框架和規(guī)范文檔。從高層次來看,OIF框架專注于解決光學(xué)和電氣通信接口共封裝的應(yīng)用領(lǐng)域和技術(shù)考量。該框架還提供了許多技術(shù)考量,用于設(shè)計能夠滿足在帶寬需求增加時降低功耗目標(biāo)的共封裝光學(xué)設(shè)備。

OIF還有一個相關(guān)的次要計劃,涉及外部激光源的使用,例如外部激光小型可插拔模塊(External Laser Small Form Pluggables,簡稱ELSFP),以延長共封裝光學(xué)設(shè)備的可靠性和使用壽命。COBO規(guī)范的主要目標(biāo)是通過為系統(tǒng)制造商、集成商、組件制造商以及8通道和16通道板載光學(xué)設(shè)備的供應(yīng)商提供通用規(guī)范,確保最終用戶能夠使用一致的技術(shù)平臺。

共封裝光學(xué)(CPO)設(shè)備的關(guān)鍵應(yīng)用領(lǐng)域

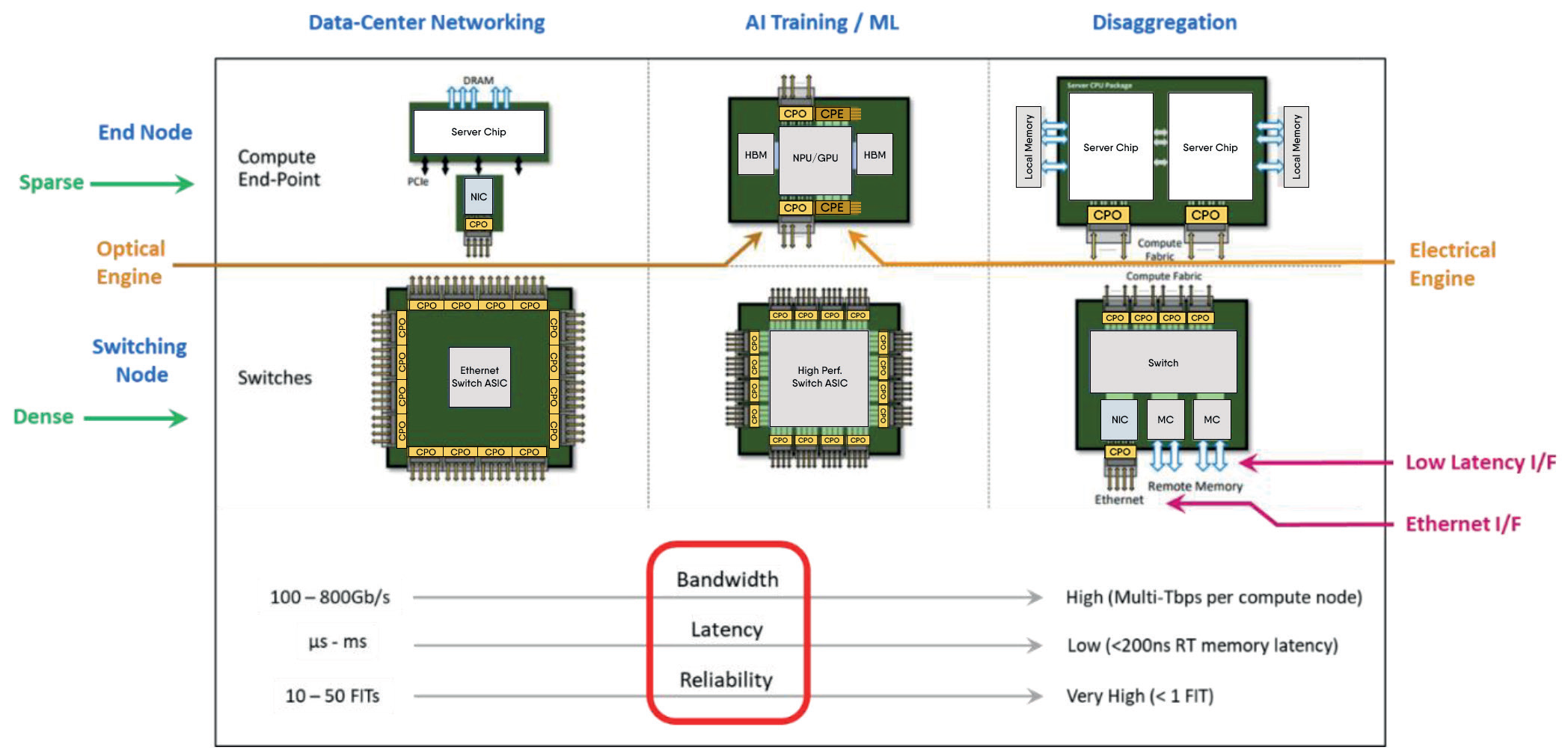

OIF確定了以下三個關(guān)鍵應(yīng)用領(lǐng)域,這些領(lǐng)域?qū)墓卜庋b光學(xué)設(shè)備提供的低功耗和高帶寬中受益匪淺:

? 數(shù)據(jù)中心以太網(wǎng)網(wǎng)絡(luò)接口控制器(NICs)、連接服務(wù)器和存儲設(shè)備的交換機(jī)

? 用于訓(xùn)練和機(jī)器學(xué)習(xí)的AI GPU接口

? Disaggregation

盡管每個應(yīng)用都有其獨特的需求,并且運(yùn)行在不同的環(huán)境中,但每個用例都有相同的架構(gòu)需求,包括兩個具有高帶寬需求的通信端點。圖2展示了如何配置共封裝光學(xué)設(shè)備以滿足這些獨特應(yīng)用的需求。

圖2: 共封裝光學(xué)設(shè)備的潛在架構(gòu),可以滿足不同應(yīng)用的帶寬、延遲和可靠性需求。來源:OIF論壇

共封裝光學(xué)設(shè)備的構(gòu)建模塊:3.2Tb/s光模塊

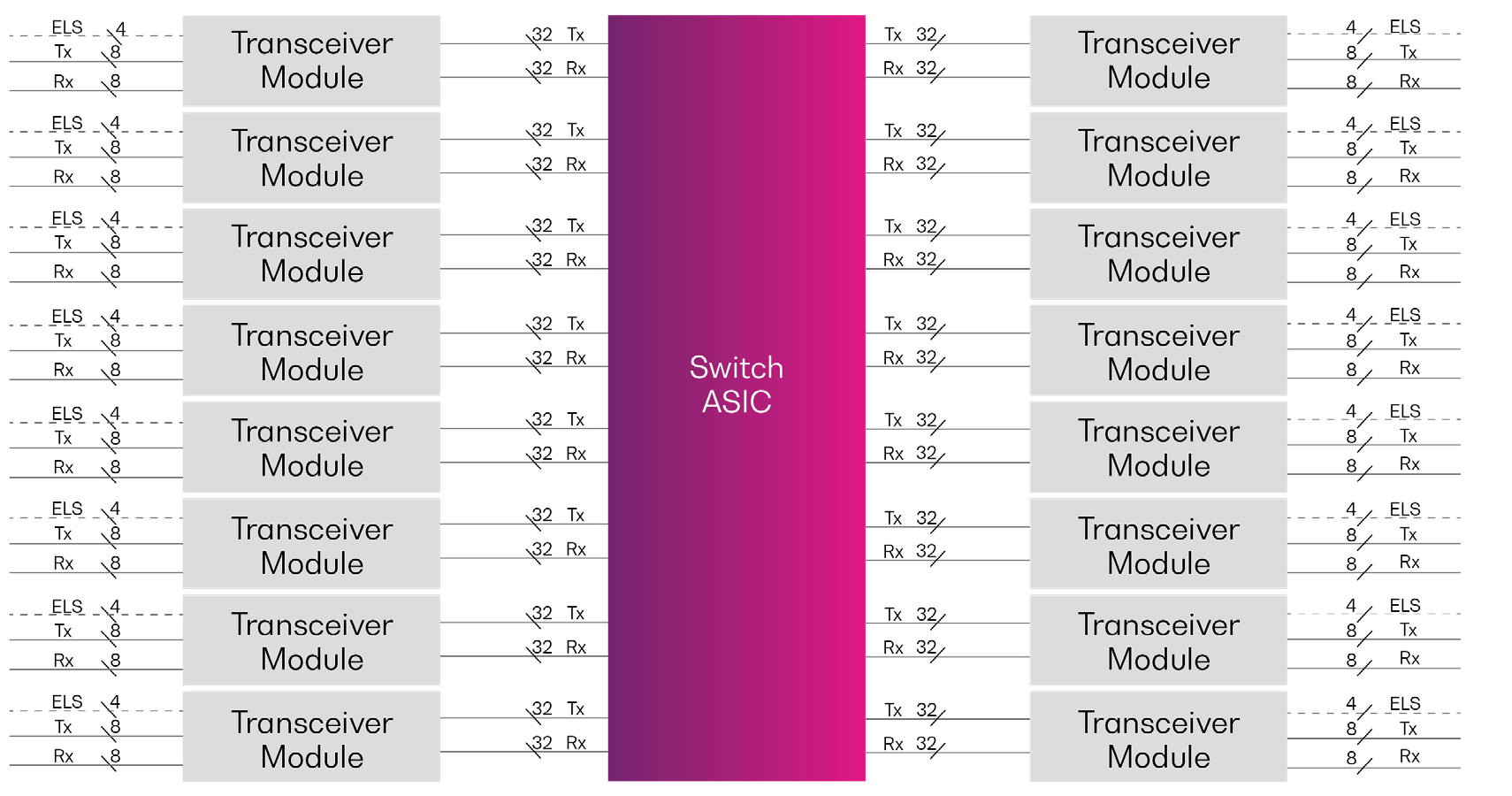

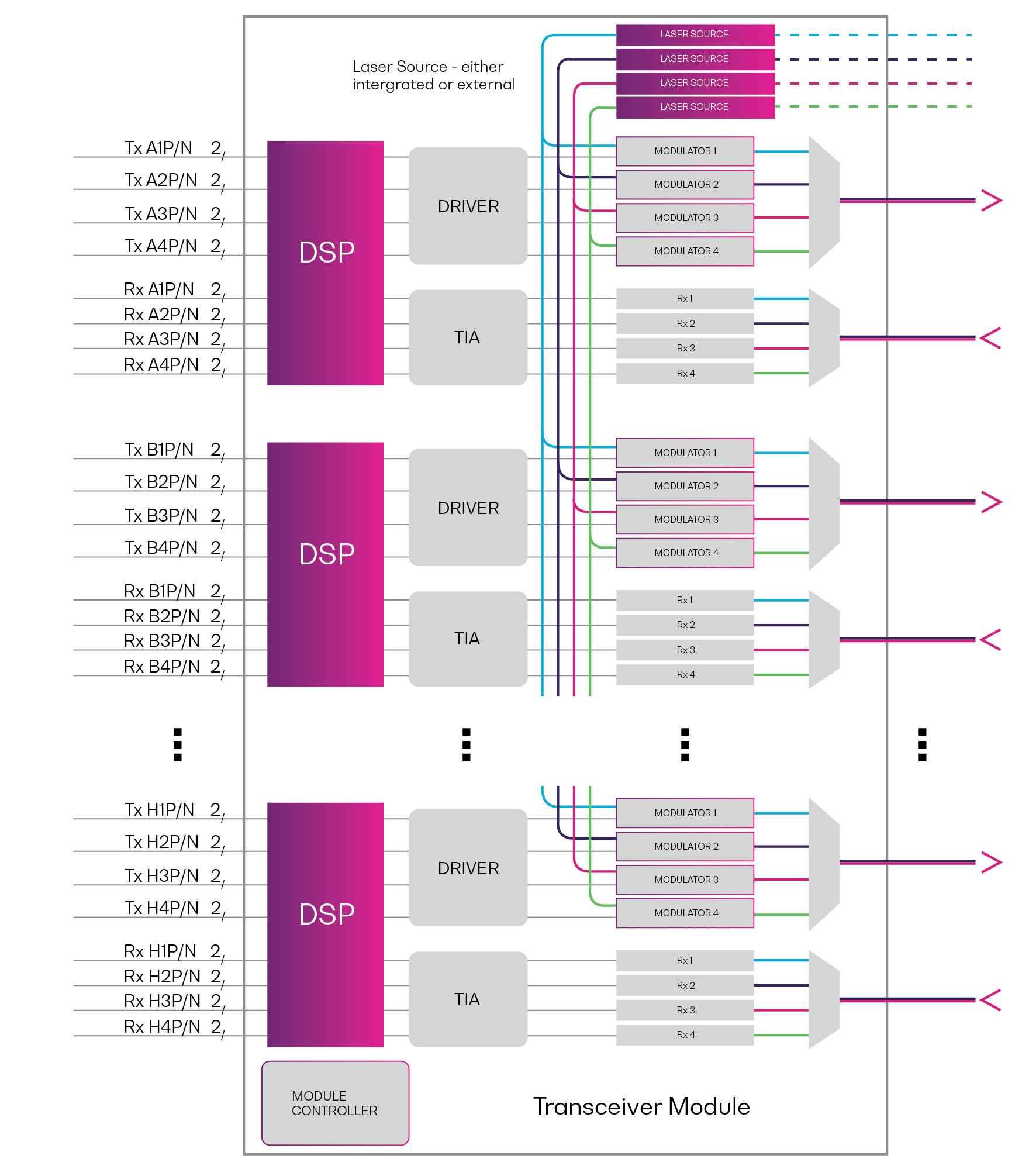

2021年,OIF啟動了一個項目,旨在為開發(fā)3.2Tb/s模塊(以及最終的6.4Tb/s模塊)提供框架,這些模塊將成為51.2Tb/s交換機(jī)的構(gòu)建模塊。最終,OIF和COBO提出的架構(gòu)基于51.2Tb/s交換機(jī),其中包括16個3.2Tb/s模塊,這些模塊被安排在ASIC附近,如圖3所示。

圖3: 400GBase-FR4 3.2Tb/s模塊的系統(tǒng)框圖

目前,許多參與3.2Tb/s共封裝光學(xué)模塊實施項目的OIF成員正在開發(fā)400GBASE-FR4和400GBASE-DR4選項,這些選項與200G接口兼容。雖然這些設(shè)備的所有要求都詳細(xì)記錄在產(chǎn)品需求文檔(PRD)中,但該項目的一些關(guān)鍵指導(dǎo)原則包括以下內(nèi)容:

? 模塊應(yīng)包括數(shù)字信號處理器(DSP)、調(diào)制驅(qū)動器、跨阻放大器(TIA)芯片以及基于硅光子學(xué)的光發(fā)射/接收組合,無論操作模式如何。

? 收發(fā)器的電氣接口應(yīng)基于32×106G電氣通道,符合CEI-112G-XSR標(biāo)準(zhǔn),電氣接口速率在200BASE-FR4操作時應(yīng)降至32×53G PAM4。

? 為了保持模塊尺寸盡可能緊湊,不應(yīng)有內(nèi)置電源單元。由于光學(xué)和電氣接口是這些模塊的關(guān)鍵組成部分,讓我們進(jìn)一步探討OIF框架為這些組件提供的指導(dǎo)。

光學(xué)接口

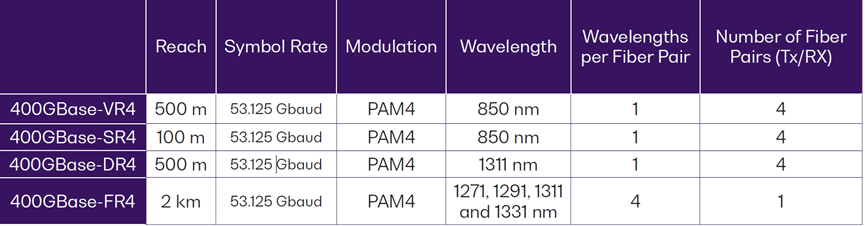

根據(jù)OIF框架,共封裝光學(xué)模塊應(yīng)基于現(xiàn)有的光學(xué)接口標(biāo)準(zhǔn),包括VR4、SR4、DR4和FR4。如表1所示,400GBase模塊具有不同的傳輸距離、波長和通道數(shù)量。根據(jù)所選標(biāo)準(zhǔn),需要不同的測試參數(shù)。

表1: 使用不同常見標(biāo)準(zhǔn)設(shè)計的光學(xué)接口規(guī)格概覽

由于這些光學(xué)接口所使用的標(biāo)準(zhǔn)與當(dāng)今可插拔模塊所使用的標(biāo)準(zhǔn)相同,因此共封裝模塊與可插拔設(shè)備之間的互操作性得以保留。因此,數(shù)據(jù)中心可以使用帶有可插拔模塊的光纖分支電纜,以實現(xiàn)可插拔模塊和共封裝模塊的最佳組合,從而滿足其需求。

電氣接口

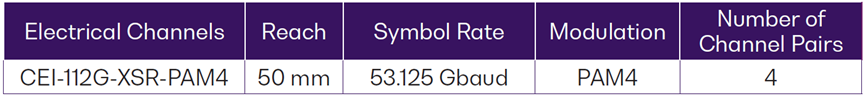

盡管共封裝應(yīng)用可能會使用多種電氣接口標(biāo)準(zhǔn),如XSR、LR、PCIe或AIB,但OIF框架主要關(guān)注使用XSR。表2中顯示了一個使用XSR的模塊示例。

表2: 使用XSR標(biāo)準(zhǔn)的模塊電氣接口規(guī)格

此外,OIF框架建議在共封裝光學(xué)模塊中可以使用以下四種電氣接口選項:

? 重定時(Retimed):使用表2中詳細(xì)描述的CEI-112G-XSR-PAM4實現(xiàn),設(shè)計用于在約50毫米的第一級封裝基板上實現(xiàn)ASIC和光引擎之間的低誤碼率通信。

? 線性放大(Linear Amplified):在引擎中消除CDR/DSP功能以降低功耗,ASIC中的發(fā)射和接收功能具有更多的放大和峰值調(diào)整,以便SerDes能夠補(bǔ)償整個鏈路。

? 半重定時(Half Retimed):引擎和ASIC通信的一半進(jìn)行重定時,另一半采用線性放大方法。

? 直接驅(qū)動(Direct Drive):這是一種簡化的接口,僅提供支持線性光通信通道所需的功能。

關(guān)于OIF框架和光模塊PRD中提出的電氣和光學(xué)接口規(guī)格的更多詳細(xì)信息,請參閱相關(guān)文檔。

共封裝光模塊激光器放置

隨著社區(qū)致力于開發(fā)3.2Tb/s模塊,關(guān)于激光器的放置位置——內(nèi)部還是外部——存在爭議。由于激光器是模塊中最容易老化且產(chǎn)生大量熱量的組件,因此在使用內(nèi)部激光器時,可靠性和系統(tǒng)散熱是需要考慮的問題。為解決可靠性問題,一個提議是在模塊中包含一個備用激光器以實現(xiàn)冗余。然而,這種方法的缺點是會增加模塊的尺寸,這對于許多應(yīng)用來說是不理想的。

OIF社區(qū)成員也在通過之前提到的ELSFP模塊項目研究激光器的外部放置。外部激光器的放置使組裝更小,消除了使用內(nèi)部激光器相關(guān)的熱挑戰(zhàn),并且通常提高了模塊的可靠性。然而,使用外部激光器的最大缺點是耦合激光進(jìn)入模塊的插入損耗會增加。為了補(bǔ)償這一點,激光器的輸出功率需要達(dá)到每個波長22dBm,這將增加能耗。

應(yīng)對共封裝光學(xué)設(shè)備的三大測試挑戰(zhàn)

新技術(shù)的開發(fā)總會為光學(xué)工程師帶來新的測試挑戰(zhàn)。為了確保新設(shè)備的快速實施和部署,從資格認(rèn)證到大批量生產(chǎn)的測試需求應(yīng)該與設(shè)備開發(fā)同步進(jìn)行。雖然本文的前半部分關(guān)注了共封裝光學(xué)設(shè)備開發(fā)的一些關(guān)鍵要素,但接下來的重點將轉(zhuǎn)向?qū)徱暽a(chǎn)這種技術(shù)所面臨的三大主要測試挑戰(zhàn)。

挑戰(zhàn)1:快速執(zhí)行組裝測試如前所述,共封裝光學(xué)設(shè)備由多個單獨的收發(fā)器模塊組成——例如,一個51.2Tb/s的共封裝設(shè)備包含16個3.2Tb/s的模塊。每個收發(fā)器模塊由來自一個或多個晶圓的芯片組裝而成。為了減少在組裝過程中后期出現(xiàn)問題的可能性,可以借鑒數(shù)十年高容量半導(dǎo)體制造的經(jīng)驗,將其應(yīng)用于共封裝光學(xué)設(shè)備所需的光測試中。讓我們來審視一下這種測試方法所需的測試階段:

? 晶圓測試

? 模塊測試

? 共封裝組裝測試

晶圓測試

晶圓測試是第一個關(guān)鍵的測試步驟,因為這是發(fā)現(xiàn)故障成本最低的環(huán)節(jié)。一旦投入資源將晶圓切割并制成模塊,制造商需要確保組成模塊的組件符合規(guī)格。為了確保沒有關(guān)鍵性能問題影響產(chǎn)量,需要在制造過程的早期進(jìn)行高吞吐量的晶圓級測試。然而,對于硅光子學(xué)的測試存在諸多挑戰(zhàn)。

盡管晶圓測試與半導(dǎo)體晶圓測試有一些相似之處,但光子測試與電子測試截然不同。例如,電學(xué)測試可以通過探針卡建立導(dǎo)電連接來完成,但對于光測試,需要精確對準(zhǔn)以將光耦合進(jìn)出光子組件。為了實現(xiàn)注入和捕獲這些測試所需的光,需要通過機(jī)器人操作光學(xué)探針在晶圓周圍移動。此外,為了在高容量下進(jìn)行這些測試,需要快速主動對準(zhǔn)。Quantifi Photonics的對數(shù)模擬功率計是專為晶圓測試設(shè)計的設(shè)備的一個例子,它允許非常快速的光纖對準(zhǔn)。

圖4:一種潛在模塊配置的示例。來源:OIF論壇。

模塊測試

模塊是通過將通過晶圓測試的芯片封裝在一起,并連接模塊所需的其他元件(如激光器、放大器、調(diào)制器和信號處理所需的基本元件)組裝而成的。模塊測試是首次有機(jī)會測試一個單元的完整性能。這可以包括多種測試,例如檢查調(diào)制光信號、激光器、熱循環(huán)以及模塊的校準(zhǔn),還可以包括在所需傳輸距離范圍內(nèi)對整個模塊進(jìn)行環(huán)回測試和誤碼率測試(BERT)。

在這一級別的測試中,可能會面臨一些挑戰(zhàn)。首先,模塊可以使用多種不同的光和電標(biāo)準(zhǔn),如本文第一部分所討論的,這意味著需要了解并測試每種模塊配置的不同性能標(biāo)準(zhǔn)。一開始,產(chǎn)量預(yù)測將決定測試站是針對單一類型的模塊(例如850nm多模的SR4)進(jìn)行定制,還是應(yīng)該能夠配置為處理多種類型(例如SR4和FR4,它們使用不同類型的光纖和波長)。

此外,在一個3.2Tb/s的模塊中,有8根光纖,每根光纖有8個波長,這意味著有64個通道需要測試。如果沒有支持并行測試的測試設(shè)備,就需要多個切換矩陣來在多光纖陣列的不同光纖之間切換,或者將不同波長切換到示波器中進(jìn)行TDEQ測量。這種切換方法不僅耗時,而且可能會增加測試成本,因為它需要時間來切換測試。

相反,支持快速并行測試的高密度測試設(shè)備(例如我們的BERT)是一種更好的測試這些模塊的方法。通過這種高密度、多通道的測試設(shè)備,用戶可以靈活地以多種方式執(zhí)行測試。例如,可以同時測試8根光纖,并對波長進(jìn)行并行測試的解復(fù)用。

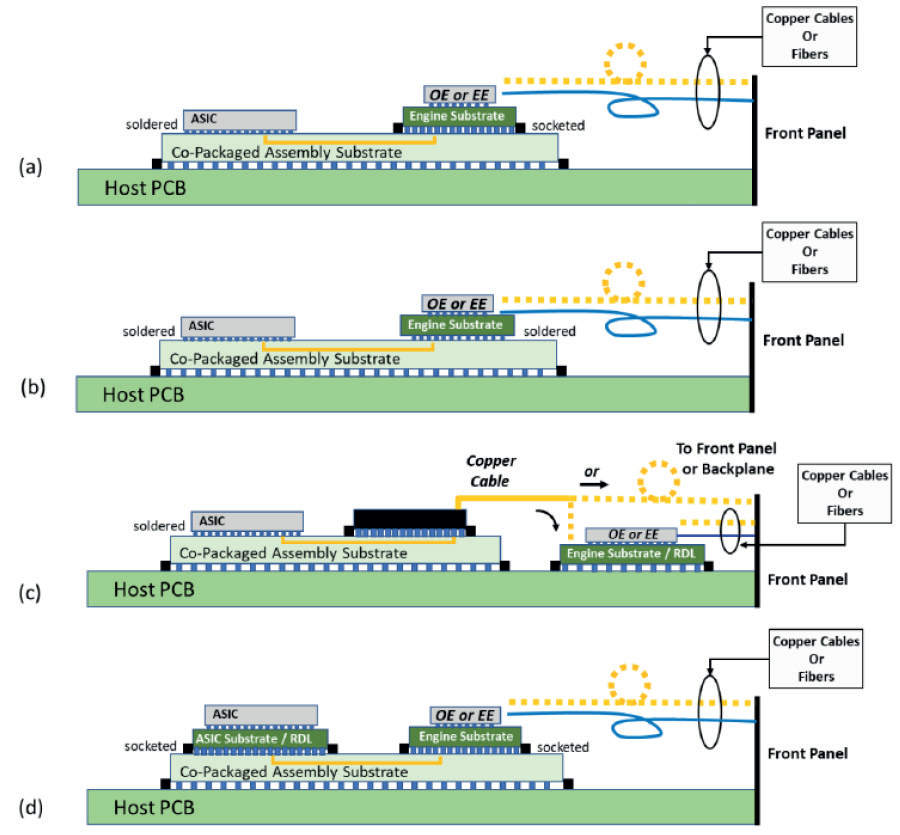

共封裝組裝測試

這一最終級別的測試涉及將經(jīng)過充分測試的模塊與ASIC和其他必要組件集成后的測試。一些可能的共封裝組件的組裝選項如圖5所示。

圖5: 共封裝光學(xué)設(shè)備的四種不同組裝選項。來源:OIF論壇

在這一點上,需要進(jìn)行功能測試,以確保所有組件都被正確集成,沒有引入制造缺陷,例如模塊錯位、光纖被夾住或端口損壞。然而,在組裝測試中,測試挑戰(zhàn)再次增加。例如,如果一個組裝件包含8個模塊,每個模塊有8根光纖和每根光纖8個波長,那么現(xiàn)在總共有512個通道需要測試。因此,如果單通道模塊測試需要一分鐘來完成,那么使用單通道測試方法測試所有512個通道是不切實際的。

因此,在生產(chǎn)線和商業(yè)測試測量供應(yīng)商努力跟上的情況下,并行測試是一個關(guān)鍵的成功因素。能夠擴(kuò)展到執(zhí)行多達(dá)288通道并行測試的高密度功率計等測試設(shè)備是進(jìn)行這些組件性能和光信號功率的快速測量所必需的。

挑戰(zhàn)2:并行組裝需要并行測試

傳統(tǒng)上,光學(xué)設(shè)備在所有組件組裝完成后才會進(jìn)行測試。雖然這種方法可以加快設(shè)備的組裝速度,但它可能導(dǎo)致需要增加測試覆蓋率,并且會對產(chǎn)量產(chǎn)生不利影響。相反,最好在設(shè)備組裝過程中進(jìn)行測試,因為這種方法可以即時提供反饋,以確保組裝成功。

讓我們來看一個簡單的例子,比較這兩種測試方法。如果使用傳統(tǒng)的“先組裝后測試”方法來組裝一個帶有MPO-24光纖帶的設(shè)備,那么在組裝過程中進(jìn)行測試可能只會對光纖帶中的一個光纖進(jìn)行測試,以確保組裝方法有效。假設(shè)這種組裝方法對其他光纖也有效,但實際上,為了優(yōu)化其中一個光纖的性能,可能會犧牲其他23個通道的性能。然而,如果使用能夠進(jìn)行并行組裝和測試的設(shè)備,就可以優(yōu)化整個光纖帶的組裝。為此,需要能夠提供多通道測試的測試儀器,例如激光器、功率計、衰減器和光開關(guān)。

挑戰(zhàn)3:消除被占用的儀器

在進(jìn)行并行測試時,確保測試儀器的最優(yōu)利用是一個棘手的問題。在并行測試操作中,很容易出現(xiàn)被占用的儀器,或者儀器在測試站中被低效使用的情況。例如,當(dāng)使用光譜分析儀(OSA)進(jìn)行測試時,可能只需要80毫秒,而使用其他儀器進(jìn)行PAM4 TDEQ測試可能需要數(shù)十秒。在這種情況下,僅需要80毫秒的儀器大部分時間可能會閑置。

為了最大化儀器利用率并降低測試系統(tǒng)的總成本,最好優(yōu)化測試流程,將串行和并行測試結(jié)合起來使用。這種測試方法需要靈活的光開關(guān)來拆分并行端口,或者同時移動并行端口,以提供從并行通道中提取某些通道或?qū)⑼ǖ酪苿铀璧撵`活性。

克服當(dāng)前的測試挑戰(zhàn)并為未來做好準(zhǔn)備

為了滿足許多應(yīng)用對帶寬需求的快速增長,同時不顯著增加能源消耗和網(wǎng)絡(luò)應(yīng)用的占地面積,共封裝光學(xué)設(shè)備是一個有前景的解決方案。盡管許多組織正在合作開發(fā)這些模塊所需的技術(shù),但必須考慮并克服這些設(shè)備當(dāng)前和未來的測試挑戰(zhàn)。

在Quantifi Photonics,我們認(rèn)識到提供高通道數(shù)、高密度測試設(shè)備的緊迫性,這將有助于推動共封裝光學(xué)設(shè)備的廣泛采用。我們已經(jīng)推出了幾款能夠滿足部分測試需求的產(chǎn)品,并制定了詳細(xì)的路線圖,以幫助解決這些測試的瓶頸問題。作為我們的愿景的一部分,我們致力于幫助光子學(xué)行業(yè)實現(xiàn)通常在電氣半導(dǎo)體測試中常見的全自動化水平。我們設(shè)想的未來是,高吞吐量測試不僅成為可能,而且使用的測試儀器還將提供方便且緊湊的形式,幫助公司繼續(xù)優(yōu)化其測試設(shè)置并快速創(chuàng)新。